# **ZnO Nanowires Synthesized by Vapor Trapping** CVD Method

Pai-Chun Chang,† Zhiyong Fan,‡ Dawei Wang,‡ Wei-Yu Tseng,‡ Wen-An Chiou,‡ Juan Hong,<sup>‡</sup> and Jia G. Lu\*,<sup>†</sup>,<sup>‡</sup>

Department of Electrical Engineering and Computer Science, and Department of Chemical Engineering and Materials Science, University of California, Irvine, California 92697

Received May 23, 2004. Revised Manuscript Received September 8, 2004

A chemical vapor deposition (CVD) process modified with vapor trapping method has been used to synthesize n-type ZnO nanowires with high carrier concentration without incorporating impurity dopants. With this method, a spatial variation of synthesis condition was created and the donors were directly introduced into the nanowires during the synthesis process. Electron microscopy and electrical transport studies show that nanowires having distinct morphologies and electrical properties were obtained at different locations in the CVD system. The vapor trapping method elucidates the effect of synthesis conditions, and provides an approach to control nanowire growth for tailorable device applications.

#### Introduction

In recent years, much effort has been invested to study quasi-one-dimensional materials because of their unique quantum properties, and their potential to be integrated into nanoscale electronic and optoelectronic devices. Nanowires of various compound semiconductors, such as GaN,  $^{1,2}In_2O_3$ ,  $^{3,4}Si_3N_4$ ,  $Ga_2O_3$ ,  $^5$  and  $MgO^6$ have been synthesized successfully. Another new system attracting increasing attention is zinc oxide (ZnO), which is a *II-VI* compound semiconductor with a wide and direct band gap of 3.37 eV at room temperature. ZnO is known to have wurtzite structure with lattice constant a = 3.249 Å, c = 5.207 Å. Its large exciton binding energy (60 meV), which is much greater than the thermal energy at room temperature, makes it a promising candidate for applications in blue-UV light emission and room-temperature UV lasing.7 Furthermore, its high piezoelectric constant ( $d_{33} = 246$ ) makes it a highly valuable material for fabricating mechanical devices, such as acoustic transducers, sensors, and actuators. 8 ZnO nanowires synthesis has been reported using many different approaches, for example sputter deposition,<sup>9</sup> template-assisted growth,<sup>10</sup> and chemical

\* Corresponding author. E-mail: jglu@uci.edu.

vapor deposition (CVD).<sup>11</sup> To improve the performance of actual electronic devices, nanowires with better electrical properties should be prepared in advance. In our experiment, we have modified the CVD synthesis process with a vapor trapping design to facilitate and control the charge carrier concentration. The as-grown nanowires exhibit *n*-type semiconducting behavior with high carrier concentration.<sup>12</sup>

### **Nanowire Synthesis**

Nanowires were synthesized via a vapor-liquid-solid (VLS) growth mechanism. 13 The VLS process took place in a horizontal quartz tube placed in a rapid thermal furnace. It had been suggested that native defects, such as zinc interstitials and oxygen vacancies, contribute to the *n*-type semiconducting behavior of ZnO, and these defects serve as donors with a binding energy of 30-60 meV.14,15 For the purpose of introducing more native defects, a quartz vial placed in the quartz tube was used to create a zinc-rich environment in the system. Because synthesis was conducted at 1 atm, the rate of zinc vapor diffusing from the vial was relatively low; therefore, a high concentration of zinc vapor was maintained inside the vial creating a high zinc concentration condition with dilute oxygen content. As a result, it yields a zinc vapor concentration decrease from inside to outside of the vial. This unique feature consequently facilitates various reaction conditions and produces a large amount of residual native defects in the ZnO nanowires.

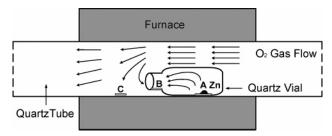

Clean silicon (Si 001) chips were prepared as substrates in the CVD system. Figure 1 shows a schematic

<sup>†</sup> Department of Electrical Engineering and Computer Science.

<sup>†</sup> Department of Chemical Engineering and Materials Science.

(1) Cheng, G. S.; Zhang, L. D.; Zhu, Y.; Fei, G. T.; Li, L.; Mo, C. M.; Mao, Y. Q. Appl. Phys. Lett. 1999, 75, 2455.

(2) Han, W.; Fan, S.; Li, Q.; Hu, Y. Science 1997, 277, 1287.

<sup>(3)</sup> Zheng, M.; Zhang, L.; Zhang, X.; Zhang, J.; Li, G. Chem. Phys.

Lett. 2001, 334, 298.

<sup>(4)</sup> Yang, H.; Shi, Q.; Tian, B.; Lu, Q.; Gao, F.; Xie, S.; Fan, F.; Yu,

C.; Tu, B.; Zhao, D. *J. Am. Chem. Soc.* **2003**, *125*, 4724.

(5) Zhang, Y.; Wang, N.; Gao, S.; He, R.; Miao, S.; Liu, J.; Zhu, J.; Zhang, X. *Chem. Mater.* **2002**, *14*, 3564.

<sup>(6)</sup> Dang, H. Y.; Wang, J.; Fan, S. S. Nanotechnology **2003**, *14*, 738. (6) Dang, H. Y.; Wang, J.; Fan, S. S. *Nanotechnology* **2000**, 17, 100.

(7) Huang, M. H.; Mao, S.; Feick, H.; Yan, H.; Wu, Y.; Kind, H.; Weber, E.; Russo, R.; Yang, P. *Science* **2001**, 292, 1897.

(8) Verghese, P. M.; Clarke, D. R. *J. Appl. Phys.* **2000**, 87, 4430.

<sup>(9)</sup> Chiou, W.; Wu, W.; Ting, J. Diamond Relat. Mater. 2003, 12, 1841.

<sup>(10)</sup> Li, Y.; Meng, G. W.; Zhang, L. D. Appl. Phys. Lett. 2000, 76,

<sup>(11)</sup> Li, S. Y.; Lee, C. Y.; Tseng, T. Y. J. Cryst. Growth 2003, 247, 357.

<sup>(12)</sup> Fan, Z.; Wang, W.; Chang, P.; Tseng, W.; Lu, G. J. unpublished research result.

<sup>(13)</sup> Hu, J.; Odom, T. W.; Lieber, C. M. Acc. Chem. Res. 1999, 32, 435

<sup>(14)</sup> Reynolds, D. C.; Look, D. C.; Jogai, B.; Litton, C. W.; Collins,

T. C.; Harsch, W.; Cantwell, G. Phys. Rev. B 1998, 57, 12 151.

(15) Look, D. C.; Hemsky, J. W. Phys. Rev. Lett. 1999, 82, 2552.

**Figure 1.** Schematic illustration of the CVD system with a horizontal quartz tube placed in a furnace. A small quartz vial inside the quartz tube is used to trap zinc vapor during the synthesis process.

illustration of the CVD furnace including a horizontal quartz tube of 1-in. diameter. In the quartz tube, Chip A was placed close to the bottom of a quartz vial, Chip B was placed at the bunghole, and Chip C was placed 2.5 cm away from the small quartz vial. Pure zinc powder (99.9% Alfa Aesar) spread on Chip A served as the raw source material. Colloidal gold (Au) nanoparticles with diameter of 30 nm deposited on both Chip B and Chip C served as catalysts in this VLS synthesis mechanism. Once the temperature went above the melting point of zinc metal (420 °C), zinc would gradually vaporize to fill the quartz vial and then diffuse to Chip B and then to Chip C. The Au nanoparticles on the silicon chips (B and C), which had formed liquid droplets, became super-saturated with zinc vapor. The nucleation of zinc oxide then began with the arrival of oxygen gas  $(O_2)$ . According to the crystal growth theory, when the droplets reached a critical radius, ZnO began to precipitate. The growth continued along one favorable direction in which the surface free energy was minimized. Synthesis was carried out in the following steps. First, the quartz tube was evacuated to  $10^{-2}$  Torr, then it was purged with Argon (Ar) gas to maintain a 1 atm inert ambient. Second, the furnace temperature was rapidly elevated to 700 °C in 10 min with a constant Ar gas flow of 90 sccm. Third, the set-point temperature (700 °C) was maintained for twenty minutes. Fourth, oxygen gas (2% concentration mixed with 98% Ar) was then flown through the quartz tube for 30 min. At the end of the process, both Chip B and Chip C appear white on the substrate surfaces.

### **Characterizations**

In this vapor trapping CVD synthesis, we arranged the two growth chips, B and C, at different positions inside the system, in order to understand the effect on growth by the variation in the zinc and oxygen concentration distribution. After synthesis, material characterizations, including electron microscopy and electrical transport measurements, were performed. The objective was to verify and distinguish the morphology change and carrier concentration difference between the nanowires grown on Chip B and Chip C.

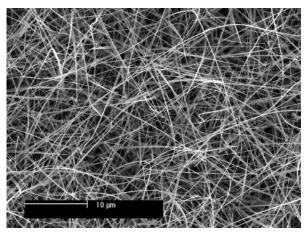

**A. Electron Microscopy.** A field emission scanning electron microscopy (FE-SEM, FEI/Philips XL-30) image (Figure 2) shows that nanowires grown on Chip C have diameters ranging from 20 to 200 nm with average length about 30  $\mu$ m. These nanowires presented on Chip C can be regarded as having been synthesized using a more traditional VLS method that many researchers have reported. We found nanowires were distributed

**Figure 2.** SEM image shows high density of ZnO nanowires grown randomly on Chip C placed outside the quartz vial.

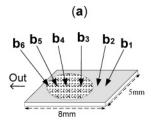

uniformly all over Chip C. In comparison, ZnO crystals were found to grow in various geometrical shapes on Chip B. Though the microstructure differences of ZnO have been well-characterized, 16 the variety obtained within such a small area on the silicon substrate with one experimental run has not been previously reported. To illustrate those differences, a series of SEM pictures (Figure 3) with same magnification (scale bar 10  $\mu$ m) has been taken from the inner edge to the outer edge of Chip B, sequentially at locations b<sub>1</sub>, b<sub>2</sub>, b<sub>3</sub>, b<sub>4</sub>, b<sub>5</sub>, and b<sub>6</sub> as indicated schematically in Figure 3a. Only locations b<sub>1</sub> and b<sub>2</sub> are from the region on the substrate where Au catalysts deposition did not reach, and therefore it was found that vapor-solid (VS) process occurred during the synthesis. As shown in Figure 3b<sub>1</sub>, a sheet of ZnO tabular crystal was formed. The inset is a zoom-in view showing the hexagonal structure crystal just nucleated and ready to grow. Figure 3b2 shows prismatic hexagonal rods of ZnO grown at b2 area. In the region where Au catalysts were deposited, wellgrown ZnO nanowires were observed at b<sub>3</sub> area (Figure 3b<sub>3</sub>). Those nanowires having diameters around 20–300 nm were very similar in geometry to the nanowires retrieved from Chip C and could be used to make nanowire devices. Moreover, moving outward to the bunghole, at region b<sub>4</sub> we found that crystals, instead of growing longer, started to grow on the surface of the nanowires because of the polarization induced growth<sup>17</sup> (Figure 3b<sub>4</sub>). Once it began to grow on the surface of individual nanowires, ZnO dendrite structures were formed, for example, comblike structure was created due to the polar surface growth shown in Figure 3b<sub>5</sub>. Because of the higher oxygen concentration at b<sub>6</sub> area, ZnO crystals grew into thicker needlelike shapes. Figure 3b<sub>6</sub> is a snapshot of the outer edge where many needlelike dendrite crystals with micrometer diameters could be found.

The variation of crystal growth on Chip B was due to the spatial change of Zn and  $O_2$  vapor pressure inside the quartz vial. The synthesis system could be simplified as a one-dimensional steady-state diffusion model from

<sup>(16)</sup> Wang, Z. L. J. Phys.: Condens. Matter 2004, 16, R829.

(17) Wang, Z. L.; Kong X. Y.; Zuo, J. M. Phys. Rev. Lett. 2003, 91, 185502.

Figure 3. (a) Six areas on Chip B substrate have been analyzed by SEM. Starting from the outer part of Chip B, locations  $b_1$ ,  $b_2$ ,  $b_3$ ,  $b_4$ ,  $b_5$ , and  $b_6$  are labeled. The shaded circle indicates the region of Au catalysts deposition. (b<sub>1</sub>) ZnO crystal sheets have just nucleated and started to grow. Inset is a closeup of the substrate surface showing the evidence of growth. (b<sub>2</sub>) ZnO rods can be seen at b<sub>2</sub> area on Chip B. Higher magnification inset with scale bar 2 µm shows clear hexagonal crystal structure of ZnO rods. (b<sub>3</sub>) Good-quality ZnO nanowires obtained at b<sub>3</sub> area. With high aspect ratio, nanowires have diameters from 20 to 300 nm and average length of  $\sim$ 20  $\mu$ m. (b<sub>4</sub>) On the surface of an individual nanorod, it can be found that ZnO crystals initially grow perpendicular to the surface. (b<sub>5</sub>) Crystals start to nucleate and grow from the surface on one single nanowire, forming a comb structure. (b<sub>6</sub>) Thick ZnO needle can be found at the outer edge. With sufficient oxygen concentration, wires with larger diameter are grown.

the fundamental mass transfer perspective.<sup>18</sup> In this model, crystal growth rate and nucleation rate are determined by zinc and oxygen vapor concentration ratio. At the inner part of the chip, oxygen had the lowest concentration and zinc had the highest vapor pressure. As a result, Chip B had a surface-reactionlimited situation dominated at inner regions (b<sub>1</sub>, b<sub>2</sub>) where the mass transfer rate was higher due to the larger Zn/O<sub>2</sub> vapor pressure ratio. On the other hand, at the outer areas (b<sub>5</sub>, b<sub>6</sub>) a lower pressure difference resulted in a higher nucleation rate that made nanowires grow into branch "buds" instead of growing longer.

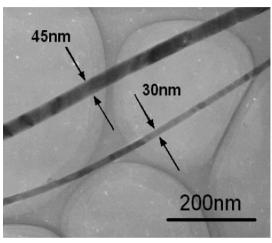

Figure 4. Transmission electron microscopy (TEM) image demonstrates two ZnO nanowires with different diameters of 30 and 45 nm. The scale bar is 200 nm.

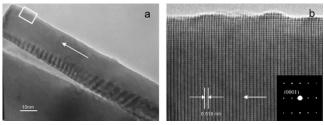

Figure 5. (a) A ZnO nanowire has about 20 nm diameter and is single-crystal grown in one direction. (b) HRTEM image of the rectangular section in Figure 5a shows ZnO crystal lattice fringes with spacing of 0.52 nm. The inset is a selected-area electron diffraction (SAED) pattern confirming the lattice spacing and the c axis [0001] is the growing direction.

The effect of mass-transfer-controlled process could thus be clearly demonstrated in the above SEM analysis. Therefore, one learns that zinc and oxygen vapor pressure difference plays an important role during synthesis, and the morphology of crystal is determined by the relative rate of surface reaction with respect to the mass transfer rate. Conclusively, to obtain highquality nanowire growth such as those obtained at location b<sub>3</sub>, it is important to balance a proper mass transfer to surface reaction ratio.

Transmission electron microscopy (TEM, FEI/Philips CM20) observation was done to examine the synthesized ZnO nanowires. A low-magnification TEM image (Figure 4) presents two ZnO nanowires with different diameters (30 and 45 nm) obtained from Chip B. The high-resolution transmission electron microscopy (HR-TEM) photos shown in Figure 5 indicate that the asgrown ZnO nanowires have single-crystal structure. Figure 5a illustrates a nanowire grown in only one direction. A high-magnification image shown in Figure 5b (taken from the rectangular box in 5a) shows lattice spacing is close to 0.52 nm. The corresponding selected area electron diffraction (SAED) pattern (insert) suggests that ZnO nanowires were growing along the [0001] lattice plane direction which is the c axis.  $^{19-21}$  Energy-

<sup>(19)</sup> Tseng, Y.; Huang, C.; Cheng, H.; Lin, I.; Liu, K.; Chen, I. Adv.

<sup>(19)</sup> Iseng, I.; Huang, C.; Cheng, H.; Lin, I.; Liu, K.; Chen, I. Aav. Funct. Mater. **2003**, 13, 811. (20) Xu, C.; Liu, Z.; Liu, S.; Wang, G. Scr. Mater. **2003**, 48, 1367. (21) Dai, L.; Chen, X. L.; Wang, W. J.; Zhou, T.; Hu, B. Q. J. Phys.: Condens. Matter **2003**, 15, 2221.

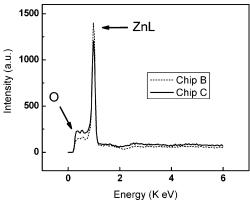

**Figure 6.** EDS showing that oxygen and zinc spectra collected from Chip B nanowires have lower O peak and higher Zn (L line) peak within energy range 0–6 keV than Chip C nanowires

dispersive X-ray spectroscopy (EDS) data acquired from two individual nanowires (one from Chip B shown in dashed line, and one from Chip C shown in solid line) shown in Figure 6 demonstrates qualitatively that Chip B nanowires have less oxygen and more zinc in composition as compared with that in Chip C. This result reveals that Chip B nanowires should have more oxygen vacancies and zinc interstitials, which are *n*-type donors.

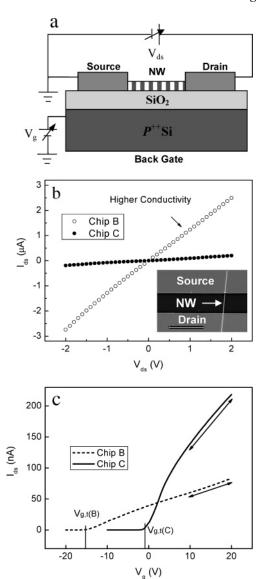

B. Electrical Properties. To investigate the electrical transport properties, ZnO nanowires were first dispersed in isopropyl alcohol and then deposited onto a  $p^{++}$  silicon chip capped with 500 nm of SiO<sub>2</sub>. The  $p^{++}$ silicon layer acted as the back-gate in the field effect transistor configuration. Photolithography was utilized to place the bi-layer metal contacts on individual ZnO nanowires. Two metals, titanium (Ti) and gold(Au), were carefully selected for the lead materials. Due to the similar work function of Ti (4.33 eV) and ZnO (4.3 eV), an Ohmic contact between the two materials can be formed which is crucial in making efficient devices. After coating with a thin layer of Ti (10 nm), the 500-nm Au layer was then deposited to complete a source-draingate three-terminal configuration shown in Figure 7a. Field effect transistors (FETs) were then fabricated using the nanowires selected from Chip B (b<sub>3</sub> region) and Chip C. Figure 7b inset is a SEM image showing a FET made by a single Chip B nanowire indicated by the white arrow.

Electrical transport measurements were conducted by sweeping  $V_{\rm ds}$  and  $V_{\rm g}$ . In general, source-drain current versus drain bias voltage  $(I_{\rm ds}-V_{\rm ds})$  was measured (Figure 7b) at zero gate voltage  $(V_{\rm g}=0)$  to estimate the conductivity of these two nanowire devices.  $I_{\rm ds}-V_{\rm ds}$  curves simply suggest that nanowires on Chip B, having more donors, yield higher electrical conductivity than those on Chip C. Based on the Drude model, assuming the entire source-drain potential was dropped across the nanowires, then we can obtain an estimate giving a lower bound of the nanowire conductivity. <sup>22</sup> The FET fabricated by Chip B nanowire has a radius  $(r_{\rm B})$  of 60 nm and channel length  $(L_{\rm B})$  of 7.6 $\mu$ m; the FET fabricated by Chip C has radius  $(r_{\rm C})$  of 44 nm and length  $(L_{\rm C})$  of 6.7 $\mu$ m. Their conductivities estimated from those

**Figure 7.** (a) Nanowire FET illustration showing the three-terminal configuration. Ti/Au was used to form metal contacts and Si–SiO $_2$  substrate served as the backgate. (b)  $I_{\rm ds}-V_{\rm ds}$  curves measured from two distinct nanowire FETs show conductivity change due to different doping concentration. Inset is a SEM image of a nanowire FET fabricated by photolithography with scale bar 10  $\mu$ m. (c) Source-drain current versus gate voltage ( $I_{\rm ds}-V_{\rm g}$ ) measurement shows that the two FETs have different threshold voltages at -15.5 and -1.3 V, respectively.

parameters are  $8.64\Omega^{-1} \text{cm}^{-1}$  and  $1.02\Omega^{-1} \text{cm}^{-1}$ , respectively. In addition, we examined whether the carrier concentration difference was indeed increased and the conductivity improvement was not merely a result of the geometry change. From the threshold voltages given in  $I_{\rm ds}-V_{\rm g}$  curves (Figure 7c), we can compute carrier concentration n using  $n=-(V_{\rm g}/e)(2\pi\epsilon\epsilon_0V_{\rm ds}/\ln(2h/r)).^{23}$  We obtain the carrier concentration of Chip B nanowire approximately  $7.46\times 10^7~{\rm cm}^{-1}$ , and that of Chip C is  $\sim 5.64\times 10^6~{\rm cm}^{-1}$  from the measured threshold voltages  $(V_{\rm g,t})-15.5~{\rm V}$  and  $-1.3~{\rm V}$ , showing a difference of one order of magnitude. Furthermore, their mobilities can also be calculated to be  $21.7~{\rm cm}^2/{\rm Vs}$  and  $80~{\rm cm}^2/{\rm Vs}$ , respectively, by the relation  $\mu_e=(dI/dV_{\rm g})/(2\pi\epsilon\epsilon_0V_{\rm ds}/L\ln v_{\rm g})$

<sup>(22)</sup> Arnold, M. S.; Avouris, P.; Pan, Z. P.; Wang, Z. L. J. Phys. Chem. B 2003, 107, 659.

$(2h/r))^{23}$  where  $V_{\rm ds}=0.1$  V,  $\epsilon=3.9,\,h=500$  nm (gate oxide layer thickness), and the transconductance values  $dI/dV_{\rm g}=2.2\times10^{-9}{\rm A/V}$  for Chip B nanowire, and  $8.29\times10^{-9}{\rm A/V}$  for Chip C can be obtained from the linear region of  $V_{\rm g}$  [10, 20 V] in the  $I_{\rm ds}-V_{\rm g}$  curves shown in Figure 7c. From the analysis above, we arrive at the fact that higher carrier concentration yields lower carrier mobility, which is due to the increased scattering from the lattice defects and electron–electron interaction.

## Summary

Zinc oxide, a widely utilized semiconductor material, is a metal oxide that has been doped often with *n*-type, *p*-type, and even ferromagnetic impurities.<sup>24,25</sup> For the purpose of fabricating nanoscale electronic devices, one emphasis is to increase nanowire channel carrier concentration and improve electrical efficiency as well. In this paper, we described a modified synthesis method

and characterized the subsequent electrical properties of ZnO nanowires. Instead of implanting other elements, our zinc vapor trapping CVD process paves a way to produce relatively high *n*-type carrier concentration in nanowires during synthesis. Electron microscopy observations show the morphology change and that singlecrystal nanowires can be obtained in certain locations with proper mass transfer to surface reasion ratio. Thus, by in-situ changing the synthesis environment, nanowires properties can be manipulated. In addition, we have fabricated nanowire FETs and made contrasts between two nanowires: one synthesized via a method similar to more traditional CVD and another synthesized under the zinc vapor trapped environment. The comparisons of their electrical transport properties conclude that the n-type behavior of the nanowires is enhanced with higher carrier concentration and better conductivity. This result contributes to the development of efficient electronic devices based on ZnO nanowires.

**Acknowledgment.** This research is supported by NSF grant ECS-0306735 and the University of California at Irvine.

CM049182C

<sup>(24)</sup> Theodoropoulou, N. A.; Hebard, A. F.; Norton, D. P.; Budai, J. D.; Boatner, L. A.; Lee, J. S.; Khim, Z. G.; Park, Y. D.; Overberg, M. E.; Pearton, S. J.; Wilson, R. G. Solid State Electron. 2003, 47, 2231. (25) Chang, Y. Q.; Wang, X. H.; Luo, X. H.; Xu, X. Y.; Chen, X. H.; Li, L.; Chen, C. P.; Wang, R. M.; Xu, J.; Yu, D. P. Appl. Phys. Lett. 2003, 83, 4020.